1Ż«ų„ę¬╠žąįŻ║

Īż┼cMCS-51 ╝µ╚▌

Īż4Kūų╣Ø┐╔ŠÄ│╠ķWĀq┤µā”Ų„

ē█├³Ż║1000īæ/▓┴裣h

öĄō■▒Ż┴¶ĢrķgŻ║10─Ļ

Īż╚½ņoæB╣żū„Ż║0Hz-24Hz

Īż╚²╝ē│╠ą“┤µā”Ų„µiČ©

Īż128*8╬╗ā╚▓┐RAM

Īż32┐╔ŠÄ│╠I/OŠĆ

Īżā╔éĆ16╬╗Č©ĢrŲ„/ėŗöĄŲ„

Īż5éĆųąöÓį┤

Īż┐╔ŠÄ│╠┤«ąą═©Ą└

ĪżĄ═╣”║─Ą─ķeų├║═Ą¶ļŖ─Ż╩Į

ĪżŲ¼ā╚š±╩ÄŲ„║═ĢrńŖļŖ┬Ę

2Ż«╣▄─_šf├„Ż║

VCCŻ║╣®ļŖļŖē║ĪŻ

GNDŻ║ĮėĄžĪŻ

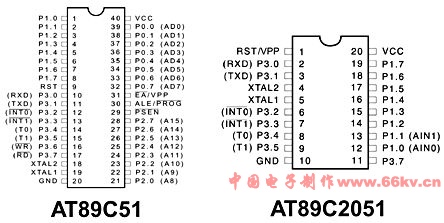

P0┐┌Ż║P0┐┌×ķę╗éĆ8╬╗┬®╝ēķ_┬ĘļpŽ“I/O┐┌Ż¼├┐─_┐╔╬³╩š8TTLķTļŖ┴„ĪŻ«öP1┐┌Ą─╣▄─_Ą┌ę╗┤╬īæ1ĢrŻ¼▒╗Č©┴x×ķĖ▀ūĶ▌ö╚ļĪŻP0─▄ē“ė├ė┌═Ō▓┐│╠ ą“öĄō■┤µā”Ų„Ż¼╦³┐╔ęį▒╗Č©┴x×ķöĄō■/ĄžųĘĄ─Ą┌░╦╬╗ĪŻį┌FIASHŠÄ│╠ĢrŻ¼P0 ┐┌ū„×ķįŁ┤a▌ö╚ļ┐┌Ż¼«öFIASH▀MąąąŻ“×ĢrŻ¼P0▌ö│÷įŁ┤aŻ¼┤╦ĢrP0═Ō▓┐▒žĒÜ▒╗└ŁĖ▀ĪŻ

P1┐┌Ż║P1┐┌╩Ūę╗éĆā╚▓┐╠ß╣®╔Ž└ŁļŖūĶĄ─8╬╗ļpŽ“I/O┐┌Ż¼P1┐┌ŠÅø_Ų„─▄Įė╩š▌ö│÷4TTLķTļŖ┴„ĪŻP1┐┌╣▄─_īæ╚ļ1║¾Ż¼▒╗ā╚▓┐╔Ž└Ł×ķĖ▀Ż¼┐╔ė├ū„ ▌ö╚ļŻ¼P1┐┌▒╗═Ō▓┐Ž┬└Ł×ķĄ═ļŖŲĮĢrŻ¼īó▌ö│÷ļŖ┴„Ż¼▀@╩Ūė╔ė┌ā╚▓┐╔Ž└ŁĄ─Šē╣╩ĪŻį┌FLASHŠÄ│╠║═ąŻ“×ĢrŻ¼P1┐┌ū„×ķĄ┌░╦╬╗ĄžųĘĮė╩šĪŻ

P2┐┌Ż║P2┐┌×ķę╗éĆā╚▓┐╔Ž└ŁļŖūĶĄ─8╬╗ļpŽ“I/O┐┌Ż¼P2┐┌ŠÅø_Ų„┐╔Įė╩šŻ¼▌ö│÷4éĆTTLķTļŖ┴„Ż¼«öP2┐┌▒╗īæĪ░1Ī▒ĢrŻ¼Ųõ╣▄─_▒╗ā╚▓┐╔Ž└ŁļŖūĶ └ŁĖ▀Ż¼Ūęū„×ķ▌ö╚ļĪŻ▓óę“┤╦ū„×ķ▌ö╚ļĢrŻ¼P2┐┌Ą─╣▄─_▒╗═Ō▓┐└ŁĄ═Ż¼īó▌ö│÷ļŖ┴„ĪŻ▀@╩Ūė╔ė┌ā╚▓┐╔Ž└ŁĄ─Šē╣╩ĪŻP2┐┌«öė├ė┌═Ō▓┐│╠ą“┤µā”Ų„╗“16╬╗ĄžųĘ═Ō▓┐öĄō■┤µ ā”Ų„▀Mąą┤µ╚ĪĢrŻ¼P2┐┌▌ö│÷ĄžųĘĄ─Ė▀░╦╬╗ĪŻį┌Įo│÷ĄžųĘĪ░1Ī▒ĢrŻ¼╦³└¹ė├ā╚▓┐╔Ž└Łā×ä▌Ż¼«öī”═Ō▓┐░╦╬╗ĄžųĘöĄō■┤µā”Ų„▀MąąūxīæĢrŻ¼P2┐┌▌ö│÷Ųõ╠ž╩Ō╣”─▄╝─┤µŲ„ Ą─ā╚╚▌ĪŻP2┐┌į┌FLASHŠÄ│╠║═ąŻ“×ĢrĮė╩šĖ▀░╦╬╗ĄžųĘą┼╠¢║═┐žųŲą┼╠¢ĪŻ ┐Śē¶ā╚╚▌╣▄└ĒŽĄĮy

P3┐┌Ż║P3┐┌╣▄─_╩Ū8éĆĦā╚▓┐╔Ž└ŁļŖūĶĄ─ļpŽ“I/O┐┌Ż¼┐╔Įė╩š▌ö│÷4éĆTTLķTļŖ┴„ĪŻ«öP3┐┌īæ╚ļĪ░1Ī▒║¾Ż¼╦³éā▒╗ā╚▓┐╔Ž└Ł×ķĖ▀ļŖŲĮŻ¼▓óė├ū„▌ö╚ļĪŻū„×ķ▌ö╚ļŻ¼ė╔ė┌═Ō▓┐Ž┬└Ł×ķĄ═ļŖŲĮŻ¼P3┐┌īó▌ö│÷ļŖ┴„Ż©ILLŻ®▀@╩Ūė╔ė┌╔Ž└ŁĄ─Šē╣╩ĪŻ

P3┐┌ę▓┐╔ū„×ķAT89C51Ą─ę╗ą®╠ž╩Ō╣”─▄┐┌Ż¼╚ńŽ┬▒Ē╦∙╩ŠŻ║

┐┌╣▄─_ éõ▀x╣”─▄

P3.0 RXDŻ©┤«ąą▌ö╚ļ┐┌Ż®

P3.1 TXDŻ©┤«ąą▌ö│÷┐┌Ż®

P3.2 /INT0Ż©═Ō▓┐ųąöÓ0Ż®

P3.3 /INT1Ż©═Ō▓┐ųąöÓ1Ż®

P3.4 T0Ż©ėøĢrŲ„0═Ō▓┐▌ö╚ļŻ®

P3.5 T1Ż©ėøĢrŲ„1═Ō▓┐▌ö╚ļŻ®

P3.6 /WRŻ©═Ō▓┐öĄō■┤µā”Ų„īæ▀x═©Ż®

P3.7 /RDŻ©═Ō▓┐öĄō■┤µā”Ų„ūx▀x═©Ż®

P3┐┌═¼Ģr×ķķWĀqŠÄ│╠║═ŠÄ│╠ąŻ“×Įė╩šę╗ą®┐žųŲą┼╠¢ĪŻ

RSTŻ║Å═╬╗▌ö╚ļĪŻ«öš±╩ÄŲ„Å═╬╗Ų„╝■ĢrŻ¼ę¬▒Ż│ųRST─_ā╔éĆÖCŲ„ų▄Ų┌Ą─Ė▀ļŖŲĮĢrķgĪŻ

ALE/PROGŻ║«öįLå¢═Ō▓┐┤µā”Ų„ĢrŻ¼Ąžųʵi┤µį╩įSĄ─▌ö│÷ļŖŲĮė├ė┌µi┤µĄžųĘĄ─Ąž╬╗ūų╣ØĪŻį┌FLASHŠÄ│╠Ų┌ķgŻ¼┤╦ę²─_ė├ė┌▌ö╚ļŠÄ│╠├}ø_ĪŻį┌ŲĮĢrŻ¼ALE Č╦ęį▓╗ūāĄ─Ņl┬╩ų▄Ų┌▌ö│÷š²├}ø_ą┼╠¢Ż¼┤╦Ņl┬╩×ķš±╩ÄŲ„Ņl┬╩Ą─1/6ĪŻę“┤╦╦³┐╔ė├ū„ī”═Ō▓┐▌ö│÷Ą─├}ø_╗“ė├ė┌Č©Ģr─┐Ą─ĪŻ╚╗Č°ę¬ūóęŌĄ─╩ŪŻ║├┐«öė├ū„═Ō▓┐öĄō■┤µā”Ų„ ĢrŻ¼īó╠°▀^ę╗éĆALE├}ø_ĪŻ╚ńŽļĮ¹ų╣ALEĄ─▌ö│÷┐╔į┌SFR8EHĄžųĘ╔Žų├0ĪŻ┤╦ĢrŻ¼ ALEų╗ėąį┌ł╠ąąMOVXŻ¼MOVCųĖ┴Ņ╩ŪALE▓┼Ųū„ė├ĪŻ┴Ē═ŌŻ¼įōę²─_▒╗┬į╬ó└ŁĖ▀ĪŻ╚ń╣¹╬ó╠Ä└ĒŲ„į┌═Ō▓┐ł╠ąąĀŅæBALEĮ¹ų╣Ż¼ų├╬╗¤oą¦ĪŻ

/PSENŻ║═Ō▓┐│╠ą“┤µā”Ų„Ą─▀x═©ą┼╠¢ĪŻį┌ė╔═Ō▓┐│╠ą“┤µā”Ų„╚ĪųĖŲ┌ķgŻ¼├┐éĆÖCŲ„ų▄Ų┌ā╔┤╬/PSENėąą¦ĪŻĄ½į┌įLå¢═Ō▓┐öĄō■┤µā”Ų„ĢrŻ¼▀@ā╔┤╬ėąą¦Ą─/PSENą┼╠¢īó▓╗│÷¼FĪŻ

/EA/VPPŻ║«ö/EA▒Ż│ųĄ═ļŖŲĮĢrŻ¼ätį┌┤╦Ų┌ķg═Ō▓┐│╠ą“┤µā”Ų„Ż©0000H-FFFFHŻ®Ż¼▓╗╣▄╩Ūʱėąā╚▓┐│╠ą“┤µā”Ų„ĪŻūóęŌ╝ė├▄ĘĮ╩Į1ĢrŻ¼ /EAīóā╚▓┐µiČ©×ķRESETŻ╗«ö/EAČ╦▒Ż│ųĖ▀ļŖŲĮĢrŻ¼┤╦ķgā╚▓┐│╠ą“┤µā”Ų„ĪŻį┌FLASHŠÄ│╠Ų┌ķgŻ¼┤╦ę²─_ę▓ė├ė┌╩®╝ė12VŠÄ│╠ļŖį┤Ż©VPPŻ®ĪŻ

XTAL1Ż║Ę┤Ž“š±╩ÄĘ┼┤¾Ų„Ą─▌ö╚ļ╝░ā╚▓┐ĢrńŖ╣żū„ļŖ┬ĘĄ─▌ö╚ļĪŻ

XTAL2Ż║üĒūįĘ┤Ž“š±╩ÄŲ„Ą─▌ö│÷ĪŻ

3Ż«š±╩ÄŲ„╠žąįŻ║

XTAL1║═XTAL2Ęųäe×ķĘ┤Ž“Ę┼┤¾Ų„Ą─▌ö╚ļ║═▌ö│÷ĪŻįōĘ┤Ž“Ę┼┤¾Ų„┐╔ęį┼õų├×ķŲ¼ā╚š±╩ÄŲ„ĪŻ╩»Š¦š±╩Ä║═╠š┤╔š±╩ÄŠ∙┐╔▓╔ė├ĪŻ╚ń▓╔ė├═Ō▓┐ĢrńŖį┤“īäėŲ„ ╝■Ż¼XTAL2æ¬▓╗ĮėĪŻėąėÓ▌ö╚ļų┴ā╚▓┐ĢrńŖą┼╠¢ę¬═©▀^ę╗éĆČ■ĘųŅlė|░lŲ„Ż¼ę“┤╦ī”═Ō▓┐ĢrńŖą┼╠¢Ą─├}īƤo╚╬║╬ę¬Ū¾Ż¼Ą½▒žĒÜ▒ŻūC├}ø_Ą─Ė▀Ą═ļŖŲĮę¬Ū¾Ą─īÆČ╚ĪŻ

4Ż«ąŠŲ¼▓┴│²Ż║

š¹éĆPEROMĻć┴ą║═╚²éƵiČ©╬╗Ą─ļŖ▓┴│²┐╔═©▀^š²┤_Ą─┐žųŲą┼╠¢ĮM║ŽŻ¼▓ó▒Ż│ųALE╣▄─_╠Äė┌Ą═ļŖŲĮ10ms üĒ═Ļ│╔ĪŻį┌ąŠŲ¼▓┴▓┘ū„ųąŻ¼┤·┤aĻć┴ą╚½▒╗īæĪ░1Ī▒Ūęį┌╚╬║╬ĘŪ┐š┤µā”ūų╣Ø▒╗ųžÅ═ŠÄ│╠ęįŪ░Ż¼įō▓┘ū„▒žĒÜ▒╗ł╠ąąĪŻ

┤╦═ŌŻ¼AT89C51įOėąĘĆæB▀ē▌ŗŻ¼┐╔ęįį┌Ą═ĄĮ┴ŃŅl┬╩Ą─Śl╝■Ž┬ņoæB▀ē▌ŗŻ¼ų¦│ųā╔ĘN▄ø╝■┐╔▀xĄ─Ą¶ļŖ─Ż╩ĮĪŻį┌ķeų├─Ż╩ĮŽ┬Ż¼CPU═Żų╣╣żū„ĪŻĄ½RAMŻ¼Č©ĢrŲ„Ż¼ ėŗöĄŲ„Ż¼┤«┐┌║═ųąöÓŽĄĮy╚įį┌╣żū„ĪŻį┌Ą¶ļŖ─Ż╩ĮŽ┬Ż¼▒Ż┤µRAMĄ─ā╚╚▌▓óŪęā÷ĮYš±╩ÄŲ„Ż¼Į¹ų╣╦∙ė├Ųõ╦¹ąŠŲ¼╣”─▄Ż¼ų▒ĄĮŽ┬ę╗éĆė▓╝■Å═╬╗×ķų╣ĪŻ |